Les canaux DAC

publication: 30 décembre 2021 / mis à jour 31 décembre 2021

Caractéristiques

Les fonctionnalités de DAC sont les suivantes :

- Deux canaux DAC 8 bits

- Conversion indépendante ou simultanée dans les canaux

- Référence de tension de la broche VDD3P3_RTC

- Générateur de forme d'onde cosinus (CW)

- Capacité DMA

- Le début de la conversion peut être déclenché par le logiciel ou par SAR ADC FSM

- Peut être entièrement contrôlé par le coprocesseur ULP

Un schéma montrant la fonction du canal DAC est présenté ici:

Le diagramme montre la boîte "CW generator" dans le coin supérieur gauche du diagramme et deux transferts mux blocs routés vers le DAC avec 8 bits en entrée d'un côté et fournissant une sortie analogique dacn_out de l'autre.

Outre CW, le DAC accepte également l'entrée du DMA, pour générer une forme d'onde arbitaire, ou de Registre RTCIO_PAD_DACn_REG pour fournir une conversion ordinaire de la valeur numérique 8 bits. Les lettres "n" sur ce schéma indiquent soit 1 soit 2 car le DAC a deux canaux.

Définition en FORTH des différents registres:

\ include registersDefinition.txt \ Registers set for DAC control $3FF48484 defREG: RTCIO_PAD_DAC1_REG \ DAC1 configuration register $3FF48488 defREG: RTCIO_PAD_DAC2_REG \ DAC2 configuration register $3FF48898 defREG: SENS_SAR_DAC_CTRL1_REG \ DAC control $3FF4889c defREG: SENS_SAR_DAC_CTRL2_REG \ DAC output control $01 18 defMASK: RTCIO_PAD_PDAC1_XPD_DAC $01 22 defMASK: SENS_DAC_DIG_FORCE $03 22 defMASK: SENS_DAC_SCALE1

Structure

Les deux canaux DAC 8 bits peuvent être configurés indépendamment. Pour chaque canal DAC, la tension analogique de sortie peut être calculé comme suit :

DACn_OUT = VDD3P3_RTC · PDACn_DAC/256

- PDACn_DAC est la tension sur la broche VDD3P3_RTC (généralement 3,3 V).

- PDACn_DAC a plusieurs sources: générateur CW, registre RTCIO_PAD_DACn_REG et DMA.

Le début de la conversion est déterminé par le registre RTCIO_PAD_PDACn_XPD_DAC. le le processus de conversion lui-même est contrôlé par un logiciel ou par SAR ADC FSM.

Générateur de forme d'onde cosinus

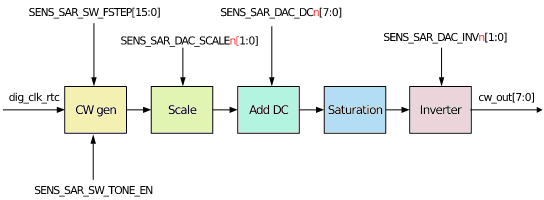

Le générateur de forme d'onde cosinus (CW) peut être utilisé pour générer une tonalité cosinus/sinus. Un diagramme montrant le cosinus La fonction du générateur de formes d'onde est présentée à la figure 2.

Le générateur CW a les caractéristiques suivantes :

- Fréquence réglable

La fréquence de CW peut être ajustée par le registre SENS_SAR_SW_FSTEP[15:0] :

freq = dig_clk_rtc_freq · SENS_SAR_SW_FSTEP/65536

La fréquence de dig_clk_rtc est généralement de 8 MHz. - Mise à l'échelle

Configuration du registre SENS_SAR_DAC_SCALEn[1:0]; l'amplitude d'un CW peut être multipliée par 1, 1/2, 1/4 ou 1/8. - Décalage CC

Le décalage peut être introduit par le registre SENS_SAR_DAC_DCn[7:0]. Le résultat sera saturé. - Déphasage

Un déphasage de 0 / 90 / 180 / 270 degrés peut être ajouté en réglant le registre SENS_SAR_DAC_INVn[1:0].

Registres

RTCIO_PAD_DAC1_REG

Registre de configuration pour DAC1

- RTCIO_PAD_PDAC1_DRV Select the drive strength of the pad. (R/W)

- RTCIO_PAD_PDAC1_HOLD Set to 1 to hold the output value on the pad; set to 0 for normal operation. (R/W)

- RTCIO_PAD_PDAC1_RDE 1: Pull-down on pad enabled; 0: Pull-down disabled. (R/W)

- RTCIO_PAD_PDAC1_RUE 1: Pull-up on pad enabled; 0: Pull-up disabled. (R/W)

- RTCIO_PAD_PDAC1_DAC PAD DAC1 output value. (R/W)

- RTCIO_PAD_PDAC1_XPD_DAC Power on DAC1. Usually, PDAC1 needs to be tristated if we power on the DAC, i.e. IE=0, OE=0, RDE=0, RUE=0. (R/W)

- RTCIO_PAD_PDAC1_MUX_SEL 0: route pad to the digital IO_MUX; (R/W) 1: route to the RTC block.

- RTCIO_PAD_PDAC1_FUN_SEL the functional selection signal of the pad. (R/W)

- RTCIO_PAD_PDAC1_SLP_SEL Sleep mode selection signal of the pad. Set this bit to 1 to put the pad to sleep. (R/W)

- RTCIO_PAD_PDAC1_SLP_IE Input enable of the pad in sleep mode. 1: enabled; 0: disabled. (R/W)

- RTCIO_PAD_PDAC1_SLP_OE Output enable of the pad. 1: enabled ; 0: disabled. (R/W)

- RTCIO_PAD_PDAC1_FUN_IE Input enable of the pad. 1: enabled it; 0: disabled. (R/W)

- RTCIO_PAD_PDAC1_DAC_XPD_FORCE Power on DAC1. Usually, we need to tristate PDAC1 if we power on the DAC, i.e. IE=0, OE=0, RDE=0, RUE=0. (R/W)

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

\ Registers set for DAC control \ DAC1 configuration register

RTCIO_PAD_DAC2_REG

DAC2 configuration register.

- RTCIO_PAD_PDAC2_DRV Sélectionnez la force d'entraînement du pin. (R/W)

- RTCIO_PAD_PDAC2_HOLD Réglez sur 1 pour maintenir la valeur de sortie sur le pin; 0 correspond au fonctionnement normal. (R/W)

- RTCIO_PAD_PDAC2_RDE 1 :déroulement sur le pad activé ; 0 : Déroulement désactivé. (R/W)

- RTCIO_PAD_PDAC2_RUE 1: Pull-up sur pad activé ; 0 : Pull-up désactivé. (R/W)

- RTCIO_PAD_PDAC2_DAC Valeur de sortie du PAD DAC2. (R/W)

- RTCIO_PAD_PDAC2_XPD_DAC Allumez le DAC2. PDAC2 doit être à trois états si nous mettons sous tension le DAC, c'est-à-dire IE=0, OE=0, RDE=0, RUE=0. (R/W)

- RTCIO_PAD_PDAC2_MUX_SEL 0: route pad vers l'IO_MUX numérique ; (R/W) 1 : route vers le bloc RTC.

- RTCIO_PAD_PDAC2_FUN_SEL Sélectionnez la fonction RTC pour ce pad. 0 : sélectionnez la fonction 0 ; 1 : sélectionnez Fonction 1.(R/W)

- RTCIO_PAD_PDAC2_SLP_SEL Signal de sélection du mode veille du pad. Réglez ce bit sur 1 pour mettre le pin en veille. (R/W)

- RTCIO_PAD_PDAC2_SLP_IE Activation de l'entrée du pad en mode veille. 1 : activé ; 0 : désactivé. (R/W)

- RTCIO_PAD_PDAC2_SLP_OE Activation de la sortie du pad. 1 : activé ; 0 : désactivé. (R/W)

- RTCIO_PAD_PDAC2_FUN_IE Validation de l'entrée du pad. 1 : activé ; 0 : désactivé. (R/W)

- RTCIO_PAD_PDAC2_DAC_XPD_FORCE Allumez le DAC2. Habituellement, nous avons besoin de tristate PDAC2 si on allume le DAC, i.e. IE=0, OE=0, RDE=0, RUE=0. (R/W)

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

\ Registers set for DAC control \ DAC2 configuration register

SENS_SAR_DAC_CTRL1_REG

Contrôle DAC.

- SENS_DAC_CLK_INV 1: inverse PDAC_CLK, 0: pas d'inversion. (R/W)

- SENS_DAC_CLK_FORCE_HIGH force PDAC_CLK à 1. (R/W)

- SENS_DAC_CLK_FORCE_LOW force PDAC_CLK à 0. (R/W)

- SENS_DAC_DIG_FORCE 1: DAC1 et DAC2 utilisent DMA, 0: DAC1 et DAC2 n'utilisent pas DMA. (R/W)

- SENS_SW_TONE_EN 1: valide le générateur CW, 0: dévalide le générateur CW. (R/W)

- SENS_SW_FSTEP Pas de fréquence du générateur CW; peut être utilisé pour ajuster la fréquence. (R/W)

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

\ Registers set for DAC control \ DAC control

SENS_SAR_DAC_CTRL2_REG

DAC output control .

- SENS_DAC_CW_EN2 1: sélection du générateur CW comme source pour PDAC2_DAC[7:0], 0: sélectionne le registre reg_pdac2_dac[7:0] comme source pour PDAC2_DAC[7:0]. (R/W)

- SENS_DAC_CW_EN1 1: sélection du générateur CW comme source pour PDAC1_DAC[7:0], 0: sélectionne le registre reg_pdac1_dac[7:0] comme source pour PDAC1_DAC[7:0]. (R/W)

- SENS_DAC_INV2 DAC2, 00: aucune inversion de bits, 01: inversion de tous les bits, 10: inversion bits hauts MSB, 11: inversion de tous les bits sauf bits hauts MSB. (R/W)

- SENS_DAC_INV1 DAC1, 00: aucune inversion de bits, 01: inversion de tous les bits, 10: inversion bits hauts MSB, 11: inversion de tous les bits sauf bits hauts MSB. (R/W)

- SENS_DAC_SCALE2 DAC2, 00: pas de rapport; 01: rapport à 1/2; 10: rapport à 1/4; 11: rapport à 1/8. (R/W)

- SENS_DAC_SCALE1 DAC1, 00: pas de rapport; 01: rapport à 1/2; 10: rapport à 1/4; 11: rapport à 1/8. (R/W)

- SENS_DAC_DC2 décalage DC pour le générateur DAC2. (R/W)

- SENS_DAC_DC1 décalage DC pour le générateur DAC1. (R/W)

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

Warning: preg_replace_callback(): Compilation failed: unmatched closing parenthesis at offset 5916 in /home/arduinofom/esp32/application/library/My/Geshi.php on line 3410

\ Registers set for DAC control \ DAC output control

Legal: site web personnel sans commerce / personal site without seling